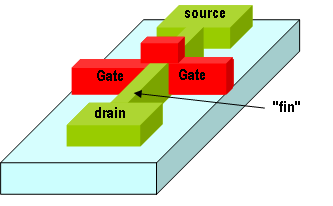

Intel's 3D tri-gate transistors have a feature size of only 22 nm. The thin structures are the silicon channels, the thicker ones are the gates and the contacts. Several gates can be used next to each other to enhance the efficiency of the switching. (c) Intel

Finally I am getting around to blog about the latest generation of transistors that Intel presented earlier this months. These transistors reach feature sizes of only 22 nanometres, down from 32 nm. To give you some perspective what this amazingly high integration means: 4,000 of those 22 nm structures fit across the width of a human hair, or similarly, 100 million of these transistors fit on the head of a pin.

Now how did they reduce transistor length scales down by almost a third? Well, even though Intel (and others) is in the business of shrinking transistor for more than 40 years, this time it’s a bit more than a mere scaling exercise. For the first time we have a commercial 3D transistor design on such a scale. In a typical ‘field-effect’ transistor, two electrical contacts are used to run an electric current through a silicon layer. The transistor is switched between an electrically conducting and an insulating state by a gate on top of the silicon. The voltage applied to that gate determines whether current can flow or not. Thereby the gate is able to set the digital ‘1’ and ‘0’ in a transistor.

A problem in shrinking transistors has been the fact that those three electric contacts need a certain minimum space of their own. Furthermore, as the gate has become smaller and smaller, it has been increasingly inefficient to switch the electric current in the silicon layer underneath. For smaller gates the electric fields from the gate just don’t reach that far down into the silicon layer.

The 3D transistor fin architecture. Image by Irene Ringworm via wikimedia.

In the new design, which isn’t only pursued by Intel but also by others, engineers now have left the flat architecture and do what architects in cities around the world have done to make use of limited real state: go vertical. As you can see from the image on the right, now the gate doesn’t only contact from the top, but wraps around a thin ‘fin’ of silicon.

This design has several advantages. It not only takes up less space, but contacting the silicon channel from three sides also means that the transistors are faster to switch. The Intel transistors can be switched up to a hundred billion times a second. And finally, the electrical fields from the gate have a more immediate effect on the current through the fin. That means that the voltage that needs to be applied to the gate is much lower, which saves up to 50% in active power.

The technology roadmap suggests a further reduction in size to 14 nm by 2013, and to 10 nm by 2015(!). And looking at the fin structures, it seems possibly to squeeze them further together, provided that the lithography processes used to make such structures can keep up.

So, the big question is, how are the alternatives to silicon transistors in light of this tough competition?

Well, there is a 2007 Nature paper by James Heath and colleagues from Caltech, that reports a device with a 1011 bits per square centimetre storage density based on crossing nanowires. These nanowires are 16 nm wide, and 33 nm spaced apart. That means storage densities seem still higher than the latest silicon transistors, but on the other hand this is unproven technology with quite a few errors across the chip, and limited life times.

And as for graphene? Looking on some of the fastest graphene devices made so far, well these have channel lengths of 140 nm, although I am sure this can be further reduced. The bond length between carbon atoms is 0.14 nanometers, so graphene could be scaled to similar sizes as those transistors. The only problem is that the edges of graphene at these length scales could mean a far more erratic behaviour in transistor operation, so I’d be hesitant to see the big potential yet.

Indeed, it seems that none of these technologies offers a compelling alternative to silicon so far. Of course, silicon has all the advantages of an entrenched technology. You can beat silicon only if you’re considerably ahead of the trend for silicon transistors, and offer a more cost-efficient solution. But seeing this latest progress in 3D transistor designs, the air is certainly getting thinner for the contenders for silicon’s crown. Perhaps it will still be possible to improve on silicon in terms of speed and power consumption, but it seems unlikely it will happen on size.

Disclaimer: I declare no competing financial interests (in particular, I don’t hold Intel stocks)

References:

Green, J., Wook Choi, J., Boukai, A., Bunimovich, Y., Johnston-Halperin, E., DeIonno, E., Luo, Y., Sheriff, B., Xu, K., Shik Shin, Y., Tseng, H., Stoddart, J., & Heath, J. (2007). A 160-kilobit molecular electronic memory patterned at 1011 bits per square centimetre Nature, 445 (7126), 414-417 DOI: 10.1038/nature05462

Liao, L., Lin, Y., Bao, M., Cheng, R., Bai, J., Liu, Y., Qu, Y., Wang, K., Huang, Y., & Duan, X. (2010). High-speed graphene transistors with a self-aligned nanowire gate Nature, 467 (7313), 305-308 DOI: 10.1038/nature09405

May 26, 2011 at 14:29

An excellent post and mirrors what we have been seeing, in that after 10 years of nanotech enabled challengers such as IBM’s Millipede and various attempts at carbon nanotube based memory (NRAM) not one has come remotely close to silicon.

I suspect that what we will see is new technologies beginning to occupy niches where they can compete on price, power consumption or added functionality (though rarely on raw performance) for specific applications. Perhaps silicon will one day be replaced by novel bio inspired architectures, but for the moment its the best we have, and by quite a big margin.

May 27, 2011 at 06:21

Silicon is not broken yet and materials doesn’t demand a fix.

The closest I can say is that only when Silicon hits a true block, other materials would stand a chance of being considered seriously.

June 7, 2011 at 03:23

Thank you for blogging, I enjoy your matter topics immensely.

You speak of elemental silicon, germanium has higher electron mobility, and compound gallium arsenide even higher electron mobility, can this element and this compound compete at such scales?

June 7, 2011 at 17:50

well, that’s the question. The problem is that silicon is pretty entrenched as a technology, and the benefits may not make up for the benefits.

In graphene the problem are edge states – as the material is a 2D sheets, the zig zags of the edges in graphene exert a stronger influence on these small length scales than is the case for silicon.

As for GaAs, yes, it’s faster. But it is also a more expensive material. There have been attempts in the late 1980s early 1990s to use GaAs in computing – the most famous example being the (commercially unsuccessful) Cray-3 supercomputer. I think in the end, silicon technology was just cheaper. Back in those days, silicon dioxide was still used to insulate the gate from the channel, and this was very easy to make from the silicon wafer. Possibly, the speed advantage there just wasn’t big enough to justify costs. And that’s possibly even more the case today as devices get smaller and electrons have to travel smaller distances anyway.

November 8, 2011 at 04:07

From this article it sounds like, even when silicon *does* hit its limit (which even Intel has said is likely to happen around 2021), its successors may be nowhere near ready to pick up the torch, which could mean several stagnant years for semiconductors. Do you agree?

If so, then we should all be concerned, since a semiconductor plateau would be likely to delay the advances in neuroscience required to develop AI and radical cognitive enhancement. Combined with chronic skilled-labour shortages that are already becoming apparent, this in turn would stifle innovation in almost all fields, not just semiconductors, during the 2030s.

November 8, 2011 at 11:08

Yes, there is a natural ceiling for computer devices. Moore’s Law is basically an exponential law, and it is clear that this won’t be possible to sustain. At some stage only a few atoms will make up a transistor, and that’s where the limit with conventional computing lies. Even in a best case scenario, I reckon graphene could only extend silicon’s limit by a generation or two, so we have to be realistic about the limits in transistor size.

And look at processor speeds – there hasn’t been much process for the past couple of years! Main advances come from the infrastucture (multicore etc), and this will be even more so in future.